Dalam manufaktur semikonduktor, proses 3 nm adalah die shrink berikutnya setelah node teknologi MOSFET 5 nanometer (metal-oxide-semiconductor field-effect transistor). Pada tahun 2022, produsen chip Taiwan TSMC berencana untuk menempatkan node semikonduktor 3 nm yang disebut N3 ke dalam produksi volume pada paruh kedua tahun 2022. Proses chip 3 nm yang disempurnakan yang disebut N3e dapat mulai diproduksi pada tahun 2023. Pembuat chip Korea Selatan Samsung secara resmi menargetkan kerangka waktu yang sama dengan TSMC (per Mei 2022) dengan dimulainya produksi 3 nm pada paruh pertama tahun 2022 menggunakan teknologi proses 3GAE dan dengan proses generasi ke-2 3 nm (bernama 3GAP) untuk menyusul pada tahun 2023, sementara menurut sumber lain proses 3 nm Samsung akan debut pada tahun 2024. Pabrikan Amerika Intel berencana untuk memulai produksi 3 nm pada tahun 2023.

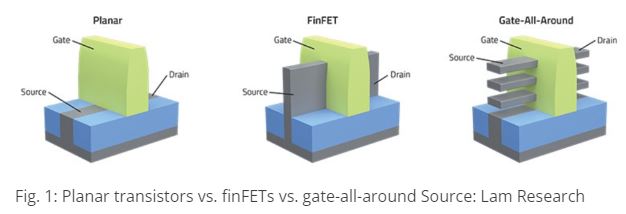

Proses 3 nm Samsung didasarkan pada teknologi GAAFET (gate-all-around field-effect transistor), sejenis teknologi MOSFET multi-gerbang, sedangkan proses 3 nm TSMC akan tetap menggunakan teknologi FinFET (fin field-effect transistor), meskipun TSMC mengembangkan transistor GAAFET. Secara khusus, Samsung berencana untuk menggunakan varian GAAFET-nya sendiri yang disebut MBCFET (transistor efek medan saluran multi-jembatan). Proses 3 nm Intel (dijuluki “Intel 3” tanpa akhiran “nm”) akan menggunakan versi teknologi FinFET yang disempurnakan, ditingkatkan, dan dioptimalkan dibandingkan dengan node proses sebelumnya dalam hal kinerja yang diperoleh per watt, penggunaan litografi dan daya EUV dan perbaikan daerah.

Istilah “3 nanometer” tidak ada hubungannya dengan fitur fisik yang sebenarnya (seperti panjang gerbang, pitch logam atau pitch gerbang) dari transistor. Menurut proyeksi yang terkandung dalam pembaruan 2021 Peta Jalan Internasional untuk Perangkat dan Sistem yang diterbitkan oleh Koneksi Industri Asosiasi Standar IEEE, simpul 3 nm diharapkan memiliki pitch gerbang yang dihubungi 48 nanometer dan pitch logam terketat 24 nanometer. Namun, dalam praktik komersial dunia nyata, “3 nm” digunakan terutama sebagai istilah pemasaran oleh masing-masing produsen microchip untuk merujuk pada chip semikonduktor silikon generasi baru yang ditingkatkan dalam hal peningkatan kerapatan transistor (yaitu tingkat miniaturisasi yang lebih tinggi), peningkatan kecepatan dan pengurangan konsumsi daya, Selain itu, tidak ada kesepakatan industri di antara produsen yang berbeda tentang nomor apa yang akan menentukan node 3 nm. Biasanya produsen chip mengacu pada node proses sebelumnya (dalam hal ini node proses 5 nm) untuk perbandingan. Misalnya, TSMC telah menyatakan bahwa chip FinFET 3 nm-nya akan mengurangi konsumsi daya sebesar 25-30% pada kecepatan yang sama, meningkatkan kecepatan sebesar 10-15% pada jumlah daya yang sama, dan meningkatkan kerapatan transistor sekitar 33% dibandingkan dengan yang sebelumnya. chip FinFET 5 nm sebelumnya. Di sisi lain, Samsung telah menyatakan bahwa proses 3 nm-nya akan mengurangi konsumsi daya sebesar 45%, meningkatkan kinerja sebesar 23%, dan mengurangi luas permukaan sebesar 16% dibandingkan dengan proses 5 nm sebelumnya.

EUV menghadapi tantangan baru pada 3 nm yang mengarah pada penggunaan multipatterning yang diperlukan.

Sumber: Wikipedia (https://en.wikipedia.org/wiki/3_nm_process)